### **MOTOROLA SEMICONDUCTOR TECHNICAL DATA**

# MJ8502 MJ8503

# **Designers Data Sheet**

#### SWITCHMODE SERIES NPN SILICON POWER TRANSISTORS

The MJ8502 and MJ8503 transistors are designed for high-voltage, high-speed, power switching in inductive circuits where fall time is critical. They are particularly suited for line operated switchmode applications such as:

- Switching Regulators

- Inverters

- Solenoid and Relay Drivers

- Motor Controls

- Deflection Circuits

Fast Turn-Off Times

150 ns Inductive Fall Time-25°C (Typ)

400 ns Inductive Crossover Time-25°C (Typ)

1200 ns Inductive Storage Time-25°C (Typ)

Operating Temperature Range -65 to + 200°C

100°C Performance Specified for:

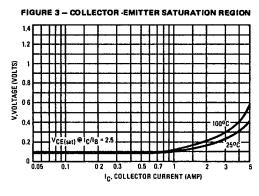

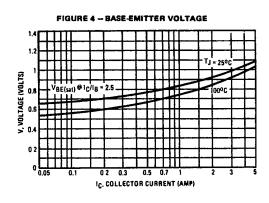

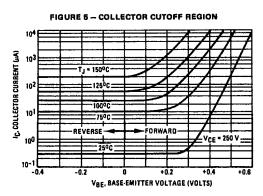

Reverse-Biased SOA with Inductive Loads Switching Times with Inductive Loads Saturation Voltages

Leakage Currents

### **MAXIMUM RATINGS**

| Rating                                                                                           | Symbol                            | MJ8502            | MJ8503            | Unit          |

|--------------------------------------------------------------------------------------------------|-----------------------------------|-------------------|-------------------|---------------|

| Collector-Emitter Voltage                                                                        | VCEO                              | 700               | 800               | Vdc           |

| Collector-Emitter Voltage                                                                        | VCEV                              | 1200              | 1400              | Vdc           |

| Emitter Base Voltage                                                                             | VEB                               | 0,8               | 8.0               | Vdc           |

| Collector Current — Continuous<br>Peak (1)                                                       | IC<br>ICM                         | 5.0<br>10         | 5.0<br>10         | Adc           |

| Base Current — Continuous<br>Peak (1)                                                            | I <sub>B</sub><br>I <sub>BM</sub> | 4.0<br>8.0        | 4.0<br>8.0        | Adc           |

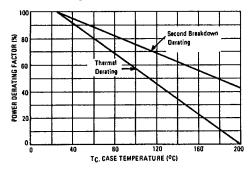

| Total Power Dissipation @ T <sub>C</sub> = 25°C<br>@ T <sub>C</sub> = 100°C<br>Derate above 25°C | ₽D                                | 150<br>86<br>0.85 | 150<br>86<br>0.85 | Watts<br>W/OC |

| Operating and Storage Junction<br>Temperature Range                                              | TJ, T <sub>stg</sub>              | -65 to +200       |                   | °C            |

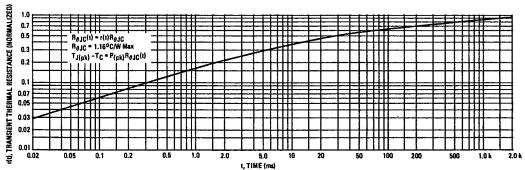

# THERMAL CHARACTERISTICS

| Characteristic                                                                | Symbol            | Max  | Unit |

|-------------------------------------------------------------------------------|-------------------|------|------|

| Thermal Resistance, Junction to Case                                          | R <sub>∂</sub> JC | 1.16 | °C/W |

| Maximum Lead Temperature for Soldering Purposes: 1/8" from Case for 5 Seconds | TL                | 275  | °C   |

| (1) Pulse Test: Pulse Width = 5 ms, Duty Cycle < 1                            | 0%.               |      |      |

#### **5.0 AMPERE**

#### **NPN SILICON POWER TRANSISTORS**

700 and 800 VOLTS 150 WATTS

#### Designer's Data for "Worst Case" Conditions

The Designers' Data Sheet permits the design of most circuits entirely from the information presented. Limit data - representing device characteristics boundaries are given to facilitate "worst case"

TOTES.

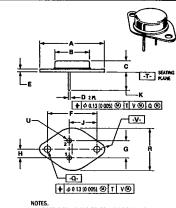

1. DIMENS'ONING AND TOLERANCING PER ANSI

Y14 SM, 1982.

2. CONTROLLING DIMENS'ON, INCH.

3. ALL RULES AND NOTES ASSOCIATED WITH

REFERENCED TO 201AA OUTLINE SHALL APPLY

| CIM | MIN       | MAX   | MiN       | MAX   |

|-----|-----------|-------|-----------|-------|

| LA. |           | 39 37 | _         | 1.550 |

| В   | _         | 21 08 | _         | 0.830 |

| _c  | 6 35      | 8 25  | 0 250     | 0 325 |

| D   | 0 97      | 1 09  | 0 038     | 0 043 |

| E   | 140       | 177   | 0.055     | 0 070 |

| F   | 30 15 BSC |       | 1.187 8SC |       |

| G   | 10 92 BSC |       | 0 430 BSC |       |

| H   | 5 46 BSC  |       | 0.215 BSC |       |

|     | 16 89 BSC |       | 0.665 BSC |       |

| LK. | 11 18     | 12.19 | 0 440     | 0 480 |

|     | 3.84      | 4 19  | 0 151     | 0 165 |

| R   | -         | 26.67 | -         | 1 050 |

| U   | 4 83      | 5.33  | 0,190     | 0.210 |

| _v_ | 3.84      | 4 19  | 0 151     | 0.165 |

|     |           |       |           |       |

MILIMETERS L INCHES

STYLE 1-PIN 1. BASE 2. EMITTER CASE COLLECTOR

> **CASE 1-06** TO-204AA (TO-3)

0.15

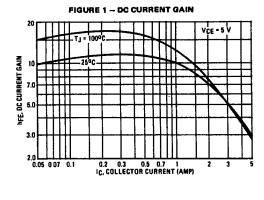

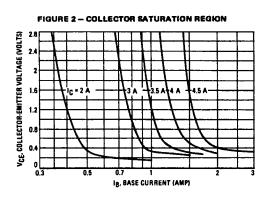

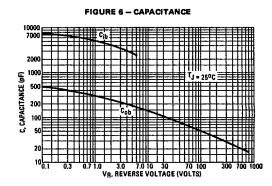

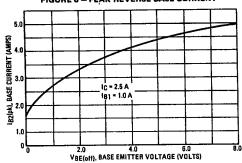

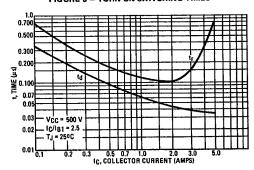

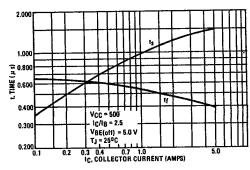

#### ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25°C unless otherwise noted) Max Unit Symbol Min Тур Characteristic OFF CHARACTERISTICS Vdc Collector-Emitter Sustaining Voltage (Table 1) MJ8502 VCEO(sus) $(I_C = 100 \text{ mA, I}_B = 0)$ MJ8503 800 mAdc Collector Cutoff Current ICEV (VCEV = Rated Value, VBE(off) = 1.5 Vdc) 0.25 5.0 (VCEV = Rated Value, VBE(off) = 1.5 Vdc, TC = 150°C) mAdc Collector Cutoff Current ICER 5.0 (V<sub>CE</sub> = Rated V<sub>CEV</sub>, R<sub>BE</sub> = 50 Ω, T<sub>C</sub> = 100°C) Emitter Cutoff Current (V<sub>EB</sub> = 7.0 Vdc, I<sub>C</sub> = 0) mAdc 10 1EB0 SECOND BREAKDOWN See Figure 12 Second Breakdown Collector Current with base forward biased <sup>I</sup>S/b RBSOA See Figure 13 Clamped Inductive SOA with Base Reverse Biased ON CHARACTERISTICS (1) OC Current Gain (IC = 1.0 Adc, VCE = 5.0 Vdc) hFE 7.5 Vdc VCE(sat) Collector-Emitter Saturation Voltage 2.0 (I<sub>C</sub> = 2.5 Adc, I<sub>B</sub> = 1.0 Adc) (I<sub>C</sub> = 5.0 Adc, I<sub>B</sub> = 2.0 Adc) 5.0 3.0 (IC = 2.5 Adc, IB = 1.0 Adc, TC = 100°C) Base-Emitter Saturation Voltage (I<sub>C</sub> = 2.5 Adc, I<sub>B</sub> = 1.0 Adc) (I<sub>C</sub> = 2.5 Adc, I<sub>B</sub> = 1.0 Adc, T<sub>C</sub> = 100°C) Vdc VBE(sat) 1.5 1.5 **DYNAMIC CHARACTERISTICS** 60 300 ρF Output Capacitance Cob (VCB = 10 Vdc, 1E = 0, ftest = 1.0 kHz) SWITCHING CHARACTERISTICS Resistive Load (Table 1) 0.040 0.20 ШS Delay Time td $(V_{CC} = 500 \, \text{Vdc}, \, \text{IC} = 2.5 \, \text{A}, \\ \text{IB1} = 1.0 \, \text{A}, \, \text{VBE(off)} = 5.0 \, \, \text{Vdc}, \, \text{tp} = 50 \, \mu \text{s}, \\$ 2.0 μs 0.125 Rise Time tr 4.0 μs Storage Time ts 1.2 Duty Cycle < 2.0%) Fall Time tf 0.65 2.0 μs Inductive Load, Clamped (Table 1) 5.0 μs Storage Time $|I_C = 2.5 \text{ A(pk)}, V_{clamp} = 500 \text{ Vdc}, I_{B1} = 1.0 \text{ A}, V_{BE(off)} = 5 \text{ Vdc}, TC = 100^{\circ}\text{C}$ tsv 1.6 2.0 μs 0.60 tc Storage Time t<sub>sv</sub> 1.2 μ3 (IC = 2.5 A(pk), V<sub>clamp</sub> = 500 Vdc, I<sub>B1</sub> = 1.0 A, \_ 0,4 μ\$. Crossover Time tç V<sub>BE(off)</sub> = 5 Vdc, T<sub>C</sub> = 25°C)

(1) Pulse Test: PW - 300 µs, Duty Cycle < 2%.

Fall Time

3-554

#### SWITCHING TIMES NOTE

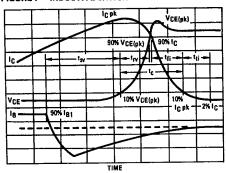

FIGURE 7 - INDUCTIVE SWITCHING MEASUREMENTS

FIGURE 8 - PEAK REVERSE BASE CURRENT

In resistive switching circuits, rise, fall, and storage times have been defined and apply to both current and voltage waveforms since they are in phase. However, for inductive loads which are common to SWITCHMODE power supplies and hammer drivers, current and voltage waveforms are not in phase. Therefore, separate measurements must be made on each waveform to determine the total switching time. For this reason, the following new terms have been defined.

t<sub>SV</sub> = Voltage Storage Time, 90% I<sub>B1</sub> to 10% VCE(pk)

trv = Voltage Rise Time, 10-90% VCE(pk)

tfi = Current Fall Time, 90-10% IC

tti = Current Tail, 10-2% IC

tc = Crossover Time, 10% VCE(pk) to 10% iC

An enlarged portion of the inductive switching waveforms is shown in Figure 7 to aid in the visual identity of these terms.

For the designer, there is minimal switching loss during storage time and the predominant switching power losses occur during the crossover interval and can be obtained using the standard equation from AN-222:  $P_{SWT} = 1/2 V_{CC} I_{C}(t_{c}) f$

In general,  $t_{rv} + t_{fi} = t_c$ . However, at lower test currents this relationship may not be valid.

As is common with most switching transistors, resistive switching is specified at 25°C and has become a benchmark for designers. However, for designers of high frequency converter circuits, the user oriented specifications which make this a "SWITCHMODE" transistor are the inductive switching speeds (tc and tsv) which are guaranteed at 100°C.

# RESISTIVE SWITCHING PERFORMANCE

FIGURE 9 - TURN-ON SWITCHING TIMES

FIGURE 10 - TURN-OFF SWITCHING TIMES

MJ8502, MJ8503

T-33-13

T-91-01

#### SAFE OPERATING AREA INFORMATION

#

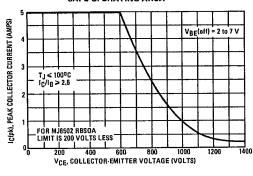

FIGURE 13 – RBSOA, REVERSE BIAS SWITCHING SAFE OPERATING AREA

#### **FORWARD BIAS**

There are two limitations on the power handling ability of a transistor: average junction temperature and second breakdown. Safe operating area curves indicate IC-VCE limits of the 'transistor that must be observed for reliable operation; i.e., the transistor must not be subjected to greater dissipation than the curves indicate.

The data of Figure 12 is based on  $T_C = 25^{\circ}C$ ;  $T_{J(pk)}$  is variable depending on power level. Second breakdown pulse limits are valid for duty cycles to 10% but must be derated when  $T_C \ge 25^{\circ}C$ . Second breakdown limitations do not derate the same as thermal limitations. Allowable current at the voltages shown on Figure 12 may be found at any case temperature by using the appropriate curve on Figure 14.

TJ(pk) may be calculated from the data in Figure 11. At high case temperatures, thermal limitations will reduce the power that can be handled to values less than the limitations imposed by second breakdown.

#### **REVERSE BIAS**

For inductive loads, high voltage and high current must be sustained simultaneously during turn-off, in most cases, with the base to emitter junction reverse biased. Under these conditions the collector voltage must be held to a safe level at or below a specific value of collector current. This can be accomplished by several means such as active clamping, RC snubbing, load line shaping, etc. The safe level for these devices is specified as Reverse Bias Safe Operating Area and represents the voltage-current condition allowable during reverse biased turn-off. This rating is verified under clamped conditions so that the device is never subjected to an avalanche mode. Figure 13 gives the complete RBSOA characteristics.

FIGURE 14 - POWER DERATING