# MM54C195/MM74C195 4-Bit Registers

## **General Description**

The MM54C195/MM74C195 CMOS 4-bit registers feature parallel inputs, parallel outputs, J-K serial inputs, shift/load control input and a direct overriding clear. The following two modes of operation are possible:

Parallel Load

Shift in direction QA towards QD

Parallel loading is accomplished by applying the four bits of data and taking the shift/load control of input low. The data is loaded into the associated flip-flops and appears at the outputs after the positive transition of the clock input. During parallel loading, serial data flow is inhibited.

Serial shifting is accomplished synchronously when the shift/load control input is high. Serial data for this mode is entered at the J-K inputs. These inputs allow the first stage to perform as a J-K, D, or T-type flip flop as shown in the truth table.

### Features

- Medium speed operation

- High noise immunity

- Low power

- Tenth power TTL compatible

- Supply voltage range

- Synchronous parallel load

- Parallel inputs and outputs from each flip-flop

- Direct overriding clear

- J and K inputs to first stage

- Complementary outputs from last stage

- Positive-edge triggered clocking

- Diode clamped inputs to protect against static charge

#### **Applications**

- Automotive

- Data terminals

- Instrumentation

- Medical electronics

- Industrial electronics

- Computers

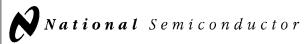

## **Schematic and Connection Diagrams**

© 1995 National Semiconductor Corporation TL/F/5902 RRD-B30M105/Printed in U. S. A.

MM54C195/MM74C195 4-Bit Registers

February 1988

8.5 MHz (typ.) with 10V supply and 50 pF load

Drive 2 LPTTL loads

0.45 V<sub>CC</sub> (typ.)

100 nW (typ.)

3V to 15V

| Office (Distribute on few sould bill be and supplied to an  |                                                                                   |                                                                     | ver Dissipation (P <sub>D</sub> )<br>Jual-In-Line | 700 mV       |            |        |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------|--------------|------------|--------|

| Voltage at                                                  |                                                                                   |                                                                     | mall Outline                                      |              |            | 500 mW |

| Operating Temperature Range Operating V <sub>CC</sub> Range |                                                                                   |                                                                     | erating V <sub>CC</sub> Range                     | 3V to 15     |            |        |

| MM54C                                                       |                                                                                   | -55°C to +125°C Abs<br>-40°C to +85°C                               | olute Maximum V <sub>CC</sub>                     |              |            | 18V    |

| MM74C                                                       | 195                                                                               | -40 C to +85 C Lea                                                  | d Temperature (Soldering,                         | 10 sec.)     | 260°C      |        |

| DC Ele                                                      | ectrical Characteris                                                              | tics Min/Max limits apply a                                         | across temperature range ur                       | nless otherw | ise noted  | I      |

| Symbol                                                      | Parameter                                                                         | Conditions                                                          | Min                                               | Тур          | Max        | Unit   |

| моѕ то сі                                                   | MOS                                                                               |                                                                     |                                                   |              |            |        |

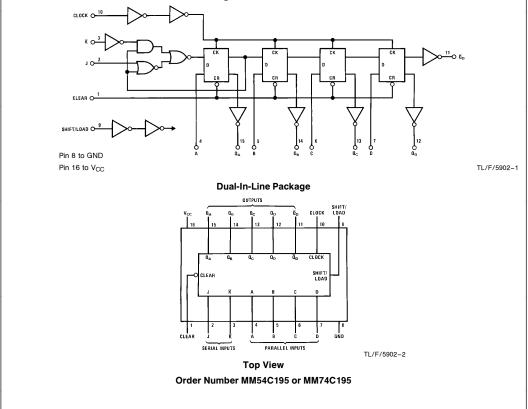

| V <sub>IN(1)</sub>                                          | Logical "1" Input Voltage                                                         | $V_{CC} = 5V$                                                       | 3.5                                               |              |            | V      |

|                                                             |                                                                                   | $V_{CC} = 10V$                                                      | 8.0                                               |              |            | V      |

| V <sub>IN(0)</sub>                                          | Logical "0" Input Voltage                                                         | $V_{CC} = 5V$                                                       |                                                   |              | 1.5        | V      |

|                                                             |                                                                                   | $V_{CC} = 10V$                                                      |                                                   |              | 2.0        | V      |

| V <sub>OUT(1)</sub>                                         | Logical "1" Output Voltage                                                        | $V_{CC} = 5V$                                                       | 4.5                                               |              |            | v      |

|                                                             | Logical i calpatitonage                                                           | $V_{CC} = 10V$                                                      | 9.0                                               |              |            | V      |

| V <sub>OUT(0)</sub>                                         | Logical "0" Output Voltage                                                        | $V_{CC} = 5V$                                                       |                                                   |              | 0.5        | v      |

|                                                             |                                                                                   | $V_{CC} = 10V$                                                      |                                                   |              | 1.0        | V      |

| I <sub>IN(1)</sub>                                          | Logical "1" Input Current                                                         | $V_{CC} = 15V$                                                      |                                                   | 0.005        | 1.0        | μA     |

| I <sub>IN(0)</sub>                                          | Logical "0" Input Current                                                         | $V_{CC} = 15V$                                                      | -1.0                                              | -0.005       |            | μA     |

|                                                             | Supply Current                                                                    | $V_{CC} = 15V$                                                      |                                                   | 0.05         | 300        | μA     |

|                                                             |                                                                                   | VCC 13V                                                             |                                                   | 0.00         | 500        | μΛ     |

|                                                             |                                                                                   |                                                                     | V 15                                              |              |            | V      |

| V <sub>IN(1)</sub>                                          | Logical "1" Input Voltage                                                         | 54C $V_{CC} = 4.5V$<br>74C $V_{CC} = 4.75V$                         | $V_{CC} - 1.5$<br>$V_{CC} - 1.5$                  |              |            |        |

| V <sub>IN(0)</sub>                                          |                                                                                   | 54C $V_{CC} = 4.5V$                                                 | •(( 1.0                                           |              | 0.0        | v      |

|                                                             | Logical "0" Input Voltage                                                         | $V_{CC} = 4.5V$<br>74C $V_{CC} = 4.75V$                             |                                                   |              | 0.8<br>0.8 | v v    |

| N/                                                          | Logical "1" Output Voltage                                                        |                                                                     | -360µA 2.4                                        |              | 0.0        | v      |

| V <sub>OUT(1)</sub>                                         |                                                                                   | 54C $V_{CC} = 4.5V, I_O = -74C V_{CC} = 4.75V, I_O =$               |                                                   |              |            | v      |

| Maximu                                                      | Logical "0" Output Valtage                                                        | 54C $V_{CC} = 4.5V, I_{O} = 3$                                      |                                                   |              | 0.1        | v      |

| V <sub>OUT(0)</sub>                                         | Logical "0" Output Voltage                                                        | $V_{CC} = 4.5V, I_O = 3$<br>74C $V_{CC} = 4.75V, I_O = 3$           | '                                                 |              | 0.4<br>0.4 | v v    |

|                                                             | IVE (See 54C/74C Family Char                                                      |                                                                     |                                                   |              | 0.1        |        |

|                                                             |                                                                                   |                                                                     |                                                   |              |            |        |

| SOURCE                                                      | Output Source Current                                                             | $V_{CC} = 5V, V_{IN(0)} = 0V$<br>$T_A = 25^{\circ}C, V_{OUT} = 0V$  | -1.75                                             |              |            | mA     |

| 1                                                           | Output Source Current                                                             |                                                                     |                                                   |              |            |        |

| SOURCE                                                      | Output Source Current                                                             | $V_{CC} = 10V, V_{IN(0)} = 0V$<br>$T_A = 25^{\circ}C, V_{OUT} = 0V$ | -8.0                                              |              |            | mA     |

| 1                                                           | Output Sink Current                                                               |                                                                     |                                                   |              |            |        |

| ISINK                                                       | Output Sink Current                                                               | $V_{CC} = 5V, V_{IN(1)} = 5V$ $T_A = 25^{\circ}C, V_{OUT} = V_{CC}$ | 1.75                                              |              |            | mA     |

| I <sub>SINK</sub>                                           | Output Sink Current                                                               | $V_{CC} = 10V, V_{IN(1)} = 10V$                                     |                                                   |              |            |        |

| SINK                                                        |                                                                                   | $T_A = 25^{\circ}C, V_{OUT} = V_{CC}$                               | 8.0                                               |              |            | mA     |

|                                                             | solute Maximum Ratings" are those value<br>meant to imply that the devices should |                                                                     |                                                   |              |            |        |

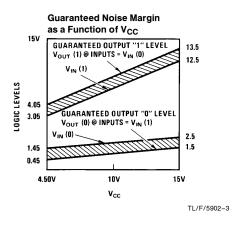

| Symbol                          | Parameter                                                                                | Conditions                      | Min        | Тур           | Max        | Units      |

|---------------------------------|------------------------------------------------------------------------------------------|---------------------------------|------------|---------------|------------|------------|

| t <sub>pd</sub>                 | Propagation Delay Time to a Logical "0" or Logical "1" from Clock to Q or $\overline{Q}$ | $V_{CC} = 5V$<br>$V_{CC} = 10V$ |            | 150<br>75     | 300<br>130 | ns<br>ns   |

| t <sub>pd</sub>                 | Propagation Delay Time to a Logical "0" or Logical "1" from Clear to Q or $\overline{Q}$ | $V_{CC} = 5V$<br>$V_{CC} = 10V$ |            | 150<br>50     | 300<br>130 | ns<br>ns   |

| t <sub>S</sub>                  | Time Prior to Clock Pulse that Data must be Present                                      | $V_{CC} = 5V$<br>$V_{CC} = 10V$ |            | 80<br>35      | 200<br>70  | ns<br>ns   |

| t <sub>S</sub>                  | Time Prior to Clock Pulse that Shift/Load<br>must be Present                             | $V_{CC} = 5V$<br>$V_{CC} = 10V$ |            | 110<br>60     | 150<br>90  | ns<br>ns   |

| t <sub>H</sub>                  | Time After Clock Pulse that Data must be Held                                            | $V_{CC} = 5V$<br>$V_{CC} = 10V$ |            | - 10<br>- 5.0 | 0<br>0     | ns<br>ns   |

| tw                              | Minimum Clear Pulse Width (t_{WL} = t_{WH})                                              | $V_{CC} = 5V$<br>$V_{CC} = 10V$ |            | 100<br>50     | 200<br>100 | ns<br>ns   |

| t <sub>W</sub>                  | Minimum Clear Pulse Width                                                                | $V_{CC} = 5V$<br>$V_{CC} = 10V$ |            | 90<br>40      | 130<br>60  | ns<br>ns   |

| t <sub>r</sub> , t <sub>f</sub> | Maximum Clock Rise and Fall Time                                                         | $V_{CC} = 5V$<br>$V_{CC} = 10V$ | 5.0<br>2.0 |               |            | μs<br>μs   |

| f <sub>MAX</sub>                | Maximum Input Clock Frequency                                                            | $V_{CC} = 5V$<br>$V_{CC} = 10V$ | 2.0<br>5.5 | 3.0<br>8.5    |            | MHz<br>MHz |

| C <sub>IN</sub>                 | Input Capacitance                                                                        | (Note 2)                        |            | 5.0           |            | pF         |

| C <sub>PD</sub>                 | Power Dissipation Capacitance                                                            | (Note 3)                        |            | 100           |            | pF         |

\*AC Parameters are guaranteed by DC correlated testing.

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Capacitance is guaranteed by periodic testing.

Note 3: C<sub>PD</sub> determines the no load AC power consumption of any CMOS device. For complete explanation see 54C/74C Family Characteristics application note AN-90.

## **Truth Table**

| Inputs AT t <sub>n</sub> |   |                 |                 |                 |                 |                                      |

|--------------------------|---|-----------------|-----------------|-----------------|-----------------|--------------------------------------|

| J                        | ĸ | Q <sub>A</sub>  | QB              | QC              | QD              | $\overline{\mathbf{Q}}_{\mathbf{D}}$ |

| L                        | Н | Q <sub>An</sub> | Q <sub>An</sub> | Q <sub>Bn</sub> | Q <sub>Cn</sub> | $\overline{Q}_{Cn}$                  |

| L                        | L | L               | Q <sub>An</sub> | Q <sub>Bn</sub> | Q <sub>Cn</sub> | Q <sub>Cn</sub>                      |

| н                        | Н | н               | Q <sub>An</sub> | Q <sub>Bn</sub> | Q <sub>Cn</sub> | Q <sub>Cn</sub>                      |

| н                        | L | Q <sub>An</sub> | Q <sub>An</sub> | Q <sub>Bn</sub> | Q <sub>Cn</sub> | Q <sub>Cn</sub>                      |

Note: H = High Level, L = Low Level

$t_n = bit time before clock pulse$

$t_{n\,+\,1}\,=\,\text{bit time after clock pulse}$

$\mathsf{Q}_{\mathsf{A}\mathsf{n}} = \, \mathsf{State} \,\, \mathsf{of} \,\, \mathsf{Q}_{\mathsf{A}} \,\, \mathsf{at} \,\, \mathsf{t}_{\mathsf{n}}$

ŧ

ŧ

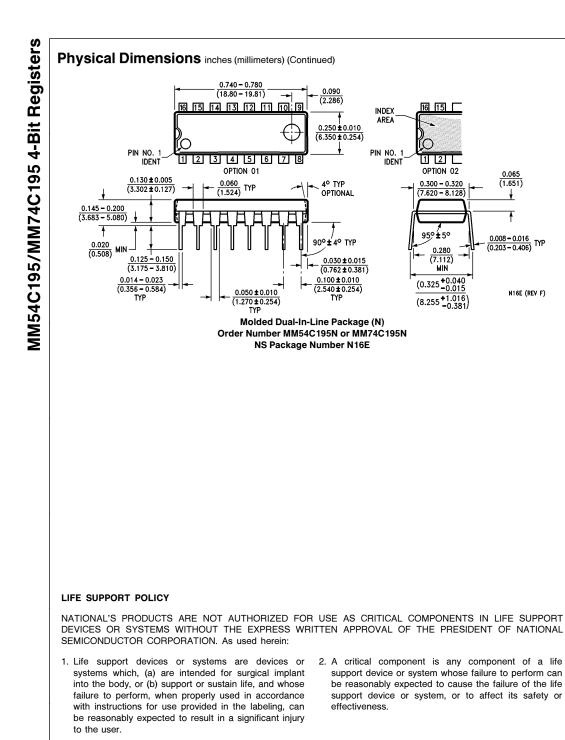

N16E (REV F)

|              | National Semiconductor | National Semiconductor              | National Semiconductor      | National Semiconducto |

|--------------|------------------------|-------------------------------------|-----------------------------|-----------------------|

| $\mathbf{N}$ | Corporation            | Europe                              | Hong Kong Ltd.              | Japan Ltd.            |

| N            | 1111 West Bardin Road  | Fax: (+49) 0-180-530 85 86          | 13th Floor, Straight Block, | Tel: 81-043-299-2309  |

|              | Arlington, TX 76017    | Email: cnjwge@tevm2.nsc.com         | Ocean Centre, 5 Canton Rd.  | Fax: 81-043-299-2408  |

|              | Tel: 1(800) 272-9959   | Deutsch Tel: (+49) 0-180-530 85 85  | Tsimshatsui, Kowloon        |                       |

|              | Fax: 1(800) 737-7018   | English Tel: (+49) 0-180-532 78 32  | Hong Kong                   |                       |

|              |                        | Français Tel: (+49) 0-180-532 93 58 | Tel: (852) 2737-1600        |                       |

|              |                        | Italiano Tel: (+49) 0-180-534 16 80 | Fax: (852) 2736-9960        |                       |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.